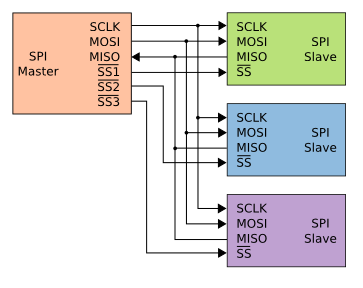

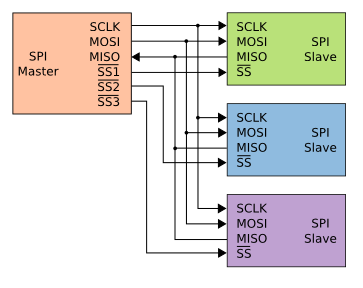

Ce module permet d'utiliser la liaison SPI des MCU AVR. Cette liaison série synchrone est constituée de 3 signaux:

- MISO: Master In Slave Out

- MOSI: Master Out Slave In

- SCLK: Serial Clock

Il s'agit d'une liaison maître-esclave. Le maître contrôle la ligne d'horloge SCLK. Pour désigner l'esclave parmi N, le maître dispose de N signaux SS (Slave Select) actifs à l'état bas.

Un maître peut contrôler plusieurs esclaves

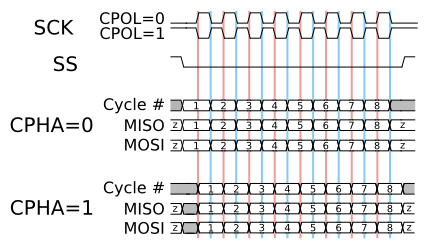

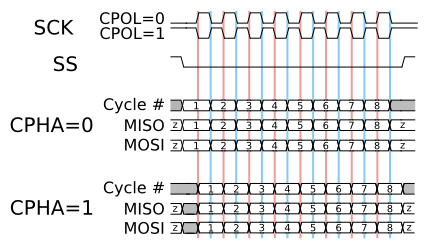

À chaque coup d'horloge le maître et l'esclave s'échangent un bit. Après huit coups d'horloges le maître a transmis un octet à l'esclave et vice versa. La vitesse de l'horloge est réglée selon des caractéristiques propres aux périphériques.

Chronologie d'un échange SPI

Les MCU AVR peuvent être maître ou/et esclave et disposent donc des broches MOSI, MISO, SCK (SCLK) et SS.

Pour utiliser ce module, il faut ajouter AVRIO_SPI_ENABLE àà la variable AVRIO_CONFIG dans le Makefile.

La configuration du module est effectuée dans le fichier avrio-board-afsk.h Ce fichier doit se trouver dans le chemin de recherche des fichiers en-tête (répertoire du projet ou dossier board normalement).

|

| enum | eSpiBitOrder { eSpiBitOrderMsb = 0,

eSpiBitOrderLsb = 1,

eSpiBitOrderNotSet = -1

} |

| | Ordre des bits. Plus de détails...

|

| |

| enum | eSpiFclkDiv {

SPI_DIV2 = 0x04,

SPI_DIV4 = 0x00,

SPI_DIV8 = 0x05,

SPI_DIV16 = 0x01,

SPI_DIV32 = 0x06,

SPI_DIV64 = 0x02,

SPI_DIV128 = 0x03

} |

| | Facteur de division de l'horloge SPI. Plus de détails...

|

| |

| enum | eSpiMode {

eSpiMode0 = (0|0),

eSpiMode1 = (0|SPI_CPHA),

eSpiMode2 = (SPI_CPOL|0),

eSpiMode3 = (SPI_CPOL|SPI_CPHA),

eSpiModeNotSet = -1

} |

| | Mode SPI. Plus de détails...

|

| |

phase horloge: 0 premier front (montant si CPOL=0), 1 deuxième front (descendant si CPOL=0)

Définition à la ligne 70 du fichier spi.h.

polarité horloge: 0 horloge sur état haut, 1 horloge sur état bas

Définition à la ligne 71 du fichier spi.h.

bit lecture-écriture pour les fonctions de la famille Reg

Définition à la ligne 72 du fichier spi.h.

Ordre des bits.

| Valeurs énumérées |

|---|

| eSpiBitOrderMsb |

MSB en premier

|

| eSpiBitOrderLsb |

LSB en premier

|

| eSpiBitOrderNotSet |

Non modifié

|

Définition à la ligne 117 du fichier spi.h.

eSpiBitOrder

Ordre des bits.

Facteur de division de l'horloge SPI.

| Valeurs énumérées |

|---|

| SPI_DIV2 |

F_SPI = (F_CPU / 2)

|

| SPI_DIV4 |

F_SPI = (F_CPU / 4)

|

| SPI_DIV8 |

F_SPI = (F_CPU / 8)

|

| SPI_DIV16 |

F_SPI = (F_CPU / 16)

|

| SPI_DIV32 |

F_SPI = (F_CPU / 32)

|

| SPI_DIV64 |

F_SPI = (F_CPU / 64)

|

| SPI_DIV128 |

F_SPI = (F_CPU / 128)

|

Définition à la ligne 78 du fichier spi.h.

eSpiFclkDiv

Facteur de division de l'horloge SPI.

Mode SPI.

Différents modes

| SPI Mode | POL | PHA | 1er front | 2ème front |

| 0 | 0 | 0 | montant, échantillonnage | descendant, changement état |

| 1 | 0 | 1 | montant, changement état | descendant, échantillonnage |

| 2 | 1 | 0 | descendant, échantillonnage | montant, changement état |

| 3 | 1 | 1 | descendant, changement état | montant, échantillonnage |

cf Wikipedia

| Valeurs énumérées |

|---|

| eSpiModeNotSet |

Non modifié

|

Définition à la ligne 105 du fichier spi.h.

| uint8_t ucSpiMasterRead |

( |

void |

| ) |

|

|

inline |

Lecture SPI.

Décale 0xFF dans le registre à décalage de l'esclave et récupère l'octet qui en sort.

- Renvoie

- Octet lu en sortie du registre à décalage de l'esclave

- Avertissement

- La broche SS de l'esclave doit être affirmée avant l'appel à cette fonction.

- Exemples:

- net/spi/demo_spi.c.

| uint8_t ucSpiMasterReadReg8 |

( |

uint8_t |

reg | ) |

|

Lecture d'un registre 8 bits.

Cette fonction réalise une transmission de l'adresse du registre à lire, suivie d'une lecture d'un octet.

- Paramètres

-

- Renvoie

- la valeur de l'octet

| uint8_t ucSpiMasterWriteRead |

( |

uint8_t |

ucByte | ) |

|

Transmission SPI.

Décale ucByte dans le registre à décalage de l'esclave et récupère l'octet qui en sort.

- Paramètres

-

| ucByte | Octet à écrire dans le registre à décalage de l'esclave (0xFF si aucun) |

- Renvoie

- Octet lu en sortie du registre à décalage de l'esclave

- Avertissement

- La broche SS de l'esclave doit être affirmée avant l'appel à cette fonction.

| void vSpiMasterReadRegBlock |

( |

uint8_t |

reg, |

|

|

uint8_t * |

buf, |

|

|

uint8_t |

len |

|

) |

| |

Lecture d'un bloc de registres.

- Paramètres

-

| reg | adresse du premier registre |

| buffer | pointeur vers la zone de stockage des octets |

| len | nombre d'octets à lire |

| void vSpiMasterWrite |

( |

uint8_t |

ucByte | ) |

|

|

inline |

Ecriture SPI.

Décale ucByte dans le registre à décalage de l'esclave.

- Paramètres

-

| ucByte | Octet à écrire dans le registre à décalage de l'esclave. |

- Avertissement

- La broche SS de l'esclave doit être affirmée avant l'appel à cette fonction.

- Exemples:

- net/spi/demo_spi.c.

| void vSpiMasterWriteReg8 |

( |

uint8_t |

reg, |

|

|

uint8_t |

data |

|

) |

| |

Ecriture d'un registre 8 bits.

- Paramètres

-

| reg | adresse du registre |

| data | valeur de l'octet |

| void vSpiMasterWriteRegBlock |

( |

uint8_t |

reg, |

|

|

const uint8_t * |

buf, |

|

|

uint8_t |

len |

|

) |

| |

Ecriture d'un bloc de registres.

- Paramètres

-

| reg | adresse du premier registre |

| buffer | pointeur vers la zone de stockage des octets |

| len | nombre d'octets à écrire |

| void vSpiMasterXfer |

( |

const uint8_t * |

tx_buffer, |

|

|

uint8_t |

tx_len, |

|

|

uint8_t * |

rx_buffer, |

|

|

uint8_t |

rx_len |

|

) |

| |

Lecture/Ecriture d'un bloc octets.

- Paramètres

-

| tx_buffer | pointeur vers la zone de stockage des octets |

| tx_len | nombre d'octets à écrire |

| rx_buffer | pointeur vers la zone de stockage des octets, la taille doit être suffisante pour y stocker le nombre d'octets demandés. |

| rx_len | nombre d'octets à lire |

Modification de l'ordre des bites.

- Paramètres

-

Modification du mode de fonctionnement.

- Paramètres

-